使用晶格畸变提高二维半导体中的载流子迁移率

二维 (2D) 半导体是具有原子级厚度的半导体材料,具有出色的电子特性。未来,这些材料有可能在众多电子和光电器件的开发中取代硅。

尽管它们具有优势,但迄今为止,二维半导体的使用受到限制,部分原因是它们在室温下的载流子迁移率低。这是由材料晶格中的声子(即与集体原子振动相关的准粒子)的强烈散射引起的。

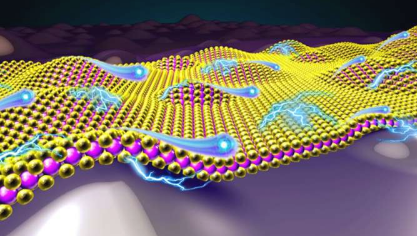

新加坡科技研究局 (A*STAR) 和中国理工大学的研究人员最近设计了一种设计策略,可以帮助克服这一限制,提高二维材料的载流子迁移率。他们提出的方法(在Nature Electronics上发表的一篇论文中进行了概述)需要在 2D 材料中引入晶格畸变,使用凸出的基板。

“我们的论文的灵感来自于 Tao Liu 等人在 2019 年在具有高表面粗糙度的基板上的二维 TMD 中观察到的高载流子迁移率,”Ming Yang 博士和 Jing Wu 博士说。进行这项研究的两名研究人员告诉 TechXplore。“然而,观察到的迁移率增强仅仅归因于应变效应,基本机制仍不清楚。为此,我们深入挖掘以解开导致迁移率显着增强的潜在物理学,并证明晶格工程是一种有效的策略来创造室温下的高性能电子设备。”

大多数提高二维半导体载流子迁移率的传统策略都依赖于获得理想的晶格结构。另一方面,Yang、Wu 和他们的同事提出的策略仅仅需要引入凸起的基板,这会在二维半导体中产生波纹并抑制声子的散射。

“我们只是将二维材料放置在具有凸起形态的基板上,在材料中产生导致晶格畸变的波纹,”杨和吴解释道。“通常,晶格畸变会对载流子迁移率产生不利影响。但是,我们表明这种晶格畸变会产生更大的电极化,这不仅可以重新调整声子的频率以有效抑制电子和声子之间的散射,还可以增强本征介电常数以进一步筛选极性声子散射。”

与增加二维半导体中载流子迁移率的其他现有方法相比,这些研究人员提出的策略既简单又具有成本效益。作为他们研究的一部分,该团队在二维二硫化钼(MoS 2 ) 上对其进行了测试,发现它导致室温载流子迁移率约为 900 cm 2 V -1 s -1,这超过了预测的平面的声子限制迁移率。 MoS 2 (范围在200和410 cm 2 V -1 s -1之间)。

“观察到的迁移率增强以及波纹-MoS 2 中如此高的载流子迁移率的潜在机制,超过了平面 MoS 2中预测的声子限制迁移率,特别值得注意,”Yang 和 Wu 说。“如此高的载流子迁移率可以为低功率电子设备铺平道路,并且是从场效应晶体管到光电探测器等大多数应用的重要参数。”

这组研究人员进行的研究突出了晶格工程策略在提高室温下电子和热电设备性能方面的巨大潜力。将来,他们的方法可用于制造基于 2D 半导体的更高效设备。此外,它可能会激发基于晶格工程的其他设计策略的发展。

“在我们接下来的研究中,我们计划系统地创建波纹/凸起的基板以最大限度地减少变异性,并研究凸起之间的相关性,”Yang 和 Wu 补充道。

免责声明:本文由用户上传,与本网站立场无关。财经信息仅供读者参考,并不构成投资建议。投资者据此操作,风险自担。 如有侵权请联系删除!

-

【别克gl8商务车怎么样】别克GL8自推出以来,凭借其出色的舒适性、空间表现和品牌口碑,成为国内高端商务用车...浏览全文>>

-

【别克gl8商务车油耗是多少】别克GL8作为一款经典的商务车型,凭借其宽敞的内部空间、舒适的乘坐体验和较高的...浏览全文>>

-

【别克gl8商务车油耗多少】别克GL8是一款非常受欢迎的中大型MPV,广泛用于商务接待、家庭出行以及出租车等场景...浏览全文>>

-

【别克gl8商务车价格多少】别克GL8作为一款经典的商务车型,凭借其舒适性、空间表现以及品牌口碑,深受企业用...浏览全文>>

-

【别克gl8商务车价格】作为一款在国内市场广受好评的中高端商务车型,别克GL8凭借其宽敞的内部空间、舒适的乘...浏览全文>>

-

【别克gl8商务车多少钱】别克GL8作为一款经典的商务车型,凭借其舒适性、空间表现和品牌口碑,在国内市场上一...浏览全文>>

-

【别克gl8商务车的参数是怎样的】作为一款在商务用车市场中备受青睐的车型,别克GL8凭借其宽敞的空间、舒适的...浏览全文>>

-

【别克gl8商务车参数】作为一款在市场上备受关注的中高端商务车型,别克GL8凭借其宽敞的空间、舒适的驾乘体验...浏览全文>>

-

【别克gl8商务车报价参数配置】别克GL8作为一款经典的商务车型,凭借其宽敞的内部空间、舒适的乘坐体验以及较...浏览全文>>

-

【别克excelle是哪款车】“别克Excelle”这一名称在汽车市场中并不常见,可能是对别克某款车型的误写或翻译差...浏览全文>>